システム奮闘記:その103

(2014年3月4日に掲載)

メモリに関心がなかった パソコンのメモリ。 搭載量が少ないと、動きが悪い。 そこで増設するのだが、色々型式がある。 型式の意味なんて、わからへん! だった。 私が知っていたのは、以下の2点だけだった。

| メモリの型式で知っていた事 | |

|---|---|

| (1) | ピンの数 |

| (2) | ECCの有無 |

だが、それでも間違いなくメモリを購入する事はできた。 パソコンの型式をインターネットで検索すると 性能部分に メモリの型式が載っている なので、メモリの型式を書いて、パソコン関係の量販店に行き 必要なメモリ量を購入していた。 その程度の知識でも問題はなかった。 そのため、メモリの勉強をしようという気は起こらなかった。

メモリの失敗談 バルク品購入

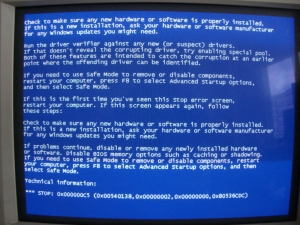

メモリ購入の失敗談を紹介します。 ヤマダ電気やヨドバシカメラなどの量販店で メモリを買っていたが、経費削減という事で2010年に パソコン工房などバルク品と呼ばれる安価なメモリを購入する事にした。 バルク品は自己責任 なのだが、そこまで悪い製品はないだろうと思ったので 何も考えずに購入した。 安いメモリを増設したパソコン。 しばらくして、使っている同僚から 画面表示のエラーが出た と言われた。

| Windows起動時に出たエラー画面 |

|---|

|

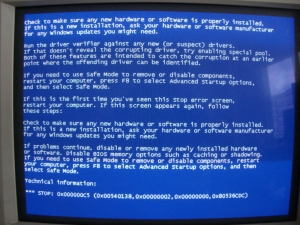

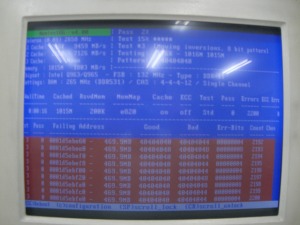

原因がわからなかった。当初、メモリを疑っていなかったが 別の同僚に「メモリかなぁ」と言われてた。 そこでメモリ検査ソフトのmemtest86+を使ってみた。 すると・・・ エラーが出まくり だった。

| memtest86+でのメモリ検査結果 |

|---|

|

|

赤い部分がエラー表示。 エラーだらけなので、メモリに障害がある事がわかる。 |

障害のあるメモリを使っていると、OSが不安定になるだけでなく

ソフトやデータに悪影響が出たりする。

そこで障害のあるメモリを取りのぞく事にした。

メモリの検査については「システム奮闘記:その86」をご覧下さい。

(オープンソース・メモリ検査ソフト memtest86+について)

この事件をキッカケに

バルク品は安かろう悪かろう

と思ってしまった。

安物買いの銭失いにならないよう、メモリはバッファローや

IO-DATAなどのメーカ製のを使う事にした。

だが、その認識は正しくなかった。

今回のメモリを話を書く事でわかった。

システム奮闘記で書いている内容は時系列で話を書くのだが、

話が飛ぶと読みにくいので、先にバルク品の話を書く事にする。

バルク品とは何かを調べてみた。

バルクの綴りは「bulk」なので、英和辞典で調べてみた。

| バルク(Bulk)とは |

|---|

|

名詞の意味で「体積」や「容量」、「多量」がある。 他にも「大半」や「大柄」もある。 |

いまいちバルク品と結び付かない。 そこでバルク品で調べてみる事にした。 バルクとは(e-Words) コンピューター部品の販売形態で使われる独特の用語だ。

| バルク(Bulk) |

|---|

|

コンピューターの部品の販売形態の一種で 業者に向けに出荷する物が、何らかの形で小売に流入した物だ。 バルク品が出回る理由は、部品メーカーが大量に在庫を抱え際の 在庫調整だったりする。 業者向けなので、箱にいれずに、包装が簡易だったり 説明書やメーカ保証が付属してなかったりする。 |

必ずしも・・・

バルク品は安かろう悪かろう

ではなかったのだ。

だが、調べてみると、バルク品を購入する際には注意が必要だ。

| バルク品(Bulk)購入の注意点 |

|---|

|

日本市場では品質が満たされない物などが安く流通している場合があり バルク品の中には粗悪な物もある そのためパソコン工房などでは「自己責任で購入」というわけだ。 |

安全な物を買う場合には、どんなメモリが良いのか。 調べてみると JEDEC準拠のメモリ を買うのが無難だ。 ところで・・・ JEDECって何やねん? 調べてみると、半導体部品の分野で規格の標準化を行なっている団体だ。 今まで、そんな事、知らなかった。 ただ、メモリの入れ物を見るとJEDECの文字があった。

| JEDEC準拠が書かれているメモリの入れ物 |

|---|

|

安全性を考える上で、メーカに加えて、JEDEC準拠かどうかが 重要な点だというのがわかった。 さてさて、バルク品を購入した失敗があったにも関らず 必要に迫られなかったので、メモリのついて、勉強する気は起こらなかった。

転機が訪れた だが、2013年、ある勘違いからメモリの勉強を行う事になった。 サーバーのメモリを購入しようと考えた。 その時、ふと思った。 このサーバーのメモリはECC付やん! 実は、別のマシンのメモリと勘違いをしていたのだが ECC付メモリと思い込んでいたので、何も気にせずに 価格コムなどで価格を調べる事にした。 だが、メモリの性能部分でRegistered対応の有無を見た瞬間・・・ Registeredとは何やねん・・・ だった。 そこで検索サイトで調べてみる事になった。 Registered対応のメモリとは

| Registered機能とは(上のサイトより引用) |

|---|

|

チップセットから出力されたアドレス信号と コントロール信号が、一時的にRegistered bufferと呼ばれる ICチップに一旦取り込まれ、bufferと呼ばれる、 信号を安定強化させる回路と、クロック信号のタイミングに合わせる ラッチ回路を通って出力される。 |

全然、わからへん (TT)

なのだ。

そしてRegistered機能が搭載されていないECC付メモリの事を

「Unbuffered DIMM」と呼ぶのだ。

ECCの有無と、Registered機能の有無の組み合わせ表を見てみる。

| 組み合わせ表 | ||

|---|---|---|

| Registered対応 | unbuffered | |

| ECC付 | 有 | 有 |

| ECC無 | 無 | 有 |

今までメモリ購入は、ECC無しのメモリだったので Registered機能の有無を考える必要がなかった。 それだけに、この機能の事は全く知らなかった。 ECC付メモリを価格コムで調べても、販売している所は少ない。 普通に売っている感じがしなかった。 さぁ、どうしようと思いはじめた。 だが、ふと気づいた。 必要なのはECC付メモリでなかった! 最初にも書いた通り、単に私の勘違いだったのだ。 だが、ここで終わってしまう予定だった。 増設したいサーバーの仕様書を見る事にした。 するとメモリの型式が DDR2:Non-ECC 2.0GB だった。 ピンの数も何もわからない。 何のメモリを買えばエエのか、わからへん に陥った。 そこで思った。 メモリを勉強せねばならない! 近年、IT技術の話から、経営や法律に走っていた私。 技術の話が疎かになり、技術を忘れてしまうという危機感を覚えていた。 そのため、ハードウェアの勉強という事で、以下の本を読んでいた。 「チップセットの秘密」(安井健治郎:DART) メモリの話もあるので良い機会だと思った。

メモリの型式

サーバーのメモリを買いたいのだが、何の型式を買えば良いのか わからない状態だった。 ところで、メモリを見ると次のような型式になっている。

| メモリの型式 | |

|---|---|

| 型式(1) | PC-3200 DDR-400 |

| 型式(2) | PC2-6400 240pin DIMM |

「PC-XXXX」とか「DDR」などがあるが、実際、それが何を意味するのか 全く知らへん のだ。 そこでDDRから調べてみる事にした。 メモリ基礎知識 メモリの性能の説明 【レポート】 メモリ技術の解説 DDR IからDDR IIへ DDR-SDRAM 「DDR」は・・・ Double Date Rate の略語だった。 直訳すると「2倍のデータの速度」なので、DDRが出るまでのメモリに比べ 単位時間辺り2倍のデータのやりとりが可能 というのだ。 「DDR2」とは、DDRを改良し、より高速にしたメモリだ。 ところで購入したメモリは、DDR2のECC無しのメモリだ。 DDR2のメモリでも・・・ PC-XXXXの型式が出てくる この「XXXX」の値には4200や6400がある。 メモリを購入したいが、この数値がわからない。 そんな時、以下のサイトを発見した。 知ってなっとく接続規格 DDR2 SDRAM-DIMM | BUFFALO バッファロー 「XXXX」とはデータ転送速度の値で、単位はMB毎秒だ。

| 「XXXX」の値はデータ転送速度(MB/s) | |

|---|---|

| PC-4200 | 4200MB/s |

| PC-6400 | 6400MB/s |

そして、データ転送速度の違いがあっても、型式が同じであれば 互換性があるため、数値を気にしなくても良い のだ。 そのため、安心してメモリが買える事がわかった。 そして、データ転送速度が速いメモリを購入した方が良いと思い DDR2 PC-6400 を購入した。クロック数で見る型式

データ転送量で見たメモリの規格。 違うメモリを見た時、こんな表記があった。 DDR-400 になっている。 400って何やねん! この400の値を調べてみると、動作周波数の値のようだ。 単位はMHzなのだ。 だが、この時、動作周波数とクロック数と同じだと思い込んだ私。 そのため、以下のように考えた。

| 動作周波数とクロック数を混同した |

|---|

|

|

動作周波数は、あくまでも1秒間にどれくらい動作を行なう事だ この場合だと、1秒間に何ビット送信できるかだ。 一方、クロック数とは、[01」が1秒間に何回あるかの数字になる。 ちなみに、上図はDDRが出る前のSRAM時代のデータ送信だ。 |

上図のように動作周波数とクロック数が同じ場合もあれば 異なる場合もある。 だが、動作周波数とクロック数を同じと勘違いした私。 そのまま信じ込んだ状態で、データ転送速度が算出する事にした。 CPUとメモリとの間のバス幅は64ビットだ。 1度に64ビットのデータのやりとりができる。 DDRの場合、2倍のデータ転送速度のため 1クロックの間に128ビットのデータのやりとりができる。 64 × 2 × 400 = 51200 bit それを8で割ると、MB毎秒の値が出てくる 51200 ÷ 8 = 6400 MB/s となるので、PC-6400と言いたくなる。 だが、DDR-400はPC3200なので 値が違うやん・・・ だった。 そこで調べ直してみるとDDR-400の「400」は クロック数の2倍の値 だった。 DDRの場合、1クロックの間に2bitのデータが送れるため 動作周波数の2倍の値を書いているのだ。

| DDRだと1クロック間に2bitデータを送信できる |

|---|

|

|

動作周波数は、あくまでも1秒間にどれくらい動作を行なう事だ。 クロックは、[01」が1秒間に何回あるかの数字になる。 |

ピンの数について

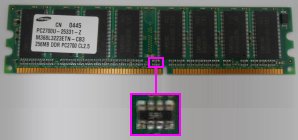

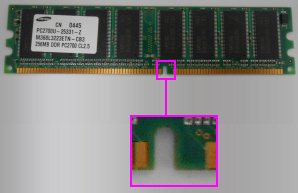

だが、この時、すっかりピンの数について調べるのを忘れていた。 後になってピンの数を調べてみる事にした。 すると・・・ DDRのピンの数は200 という記述を見た。 だが、別のサイトでは DDRのピンの数は184 という記述だった。 一体、どういう事やねん・・・ 同じ型式でもピンの数に違いがあれば、間違えて購入する問題がある。 これらを調べてみると、以下のサイトが見つけた。 メモリの規格 アイ・オ・データ機器 IODATA DDRでピンの数に違いが出るのは・・・ デスクトップ用かノート用の違い だった。 なんともズッコける結末だった。 DDRの場合、ピンの数は184個。 だが、実物を見てみる。

| メモリのピンの数 DDR PC-2700の写真 |

|---|

|

| ピンクで囲んだのがピンの部分。 |

とても184個のピンがあるとは思えへん! どういう事だろうか。 調べていくと、以下のサイトを発見した。 メモリでパソコンをスピードアップ!(バッファロー) 表と裏では別々のピンだった メモリの表面と裏面が別々のピンだった事は、今まで気にもしなかった。 断面図を撮影したかったが、上手に撮影できなかったので メモリの断面を描いてみた。

| メモリの断面図 |

|---|

|

|

メモリの表と裏は別々のピンになっている。 そのため、表の数の2倍がピンの数になるのだ。 |

そして実際に数えてみる事にした。

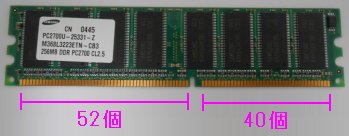

| メモリのピンの数 DDR PC-3200の場合 |

|---|

|

|

表面には52個と40個のピンがある。合計92個だ。 裏面も同じ数だけあるので、合計すると184個になる。 |

小さいだけに、結構、数えるのが大変だったが納得できた。 ところでメモリの話を見ていくと SIMMやDIMM の文字を見る。一体、どういう意味なのか調べてみた。 SIMMの略は Single Inline Memory Module だ。 直訳すると「単一差し込みメモリ部品」だ。 これだと、意味がわからないが、ピンの断面をみると、納得できる。

| SIMM時代のメモリのピンの断面 |

|---|

|

|

DIMMと違って、片方しかピンがない。 SIMMは486CPU時代のパソコンのメモリだ。 その頃のメモリのピンの数は72だったりする。 |

ちなみに、DIMMの略は

Dual Inline Memory Module

で、直訳すると「2つの差し込みメモリ部品」だ。

差し込み部分の断面を見ると、ピンが2つあるからだ。

| DIMMのメモリの断面図 |

|---|

|

|

メモリの表と裏は別々のピンになっている。 そのため、表の数の2倍がピンの数になるのだ。 |

SIMMやDIMMの名称を見た時、難しそうかなぁと思ったが そのまんまやん! という話だった。

メモリのチップ数

メモリの事を調べていると、以下のサイトを発見した。 コンピュータの基礎の基礎 Part2 RAMの物理的な内部構造は(日経ITPro) CPUとメモリ間のバス幅は64ビット。 メモリチップは4ビット、8ビットがある。 4ビットの場合は チップが16個搭載 8ビットの場合は チップが8個搭載 されているのだ。 メモリ上にあるチップの数。全く意識した事がなかった。

| メモリチップとバス幅との関係 |

|---|

|

|

メモリからデータを読み込む際、一度に64ビットが読み込まれる。 CPUからアドレス指定され、データを読み込む際 チップ8個搭載のメモリの場合、8ビット分のデータが一度に出力される。 |

実際にメモリを見てみると

ホンマに8個搭載されとる

| 8ビットチップの場合、メモリ上にチップが8個ある |

|---|

|

| チップが8個ある事から、8ビットチップだとわかる。 |

ちなみにノートパソコン用のメモリでも見てみた。

こっちも8個チップが搭載されとる

| ノートパソコンのメモリの表面 |

|---|

|

| 裏面 |

|

| 表と裏で合計8個、チップがあるのがわかる。 |

チップには4ビットもある。 その場合、16個、メモリ上にチップがあるはず。自分の目で確かめたい。 というわけで、メモリを探してみるとあった。

| 4ビットチップのメモリの表面 |

|---|

|

| 裏面 |

|

| 表と裏で合計16個、チップがあるのがわかる。 |

ところでCPUとメモリとのバス幅が64ビットになっているのに

メモリのチップは4ビットや8ビットなのか。

以下のサイトに、その理由が書いていた。

コンピュータ・アーキテクチュア第3回 藤木 文彦

互換性の意味の問題

だった。

| 2つの互換性の問題 | |

|---|---|

| ハードの側面 | そのまま8ビットのチップを使えば 新たにメモリチップやマザーボードなどの 開発・設計する手間が省ける。 |

| ソフトの側面 | 新たにソフトを開発しなくても済む。 |

まさに受け売りの内容なのだ。 自分の言葉で説明しろと言われたら、次のように反論します。 今頃、ハードウェア技術者になってます 相変わらず、忍法「開き直りの技」を使う私。

誤り訂正符号 パリティとECC

メモリにはECC無しとECC付がある。 ECCとは誤り訂正 というのは知っている。 ECCの略は Error Check and Correction なのだ。 直訳すると「誤り検出訂正」となる。 だが、メモリ内で誤りが発生しても修正する機能がある事も知っているが それ以上については 何も知らへん なのだ。 人に説明すると、すぐにメッキが剥がれる程度の知識なので 調べてみる事にした。 調べてみると、以下のサイトを発見した。 メモリ技術解説:Expressテクノロジ読本 | NEC ところが、このサイトではECCの略が Error Correction Code になっている。 システム奮闘記を連載開始時の20代後半なら、教条主義になり 「どっちが正しいねん」と思うが、40才の現在では そんな事は、どーでも良くなっている。 ところで、NECのサイトにあった略を直訳すると 「誤り訂正符号」で、そのまんまだ。 だが、NECのサイトを見ても、いまいち、ピンと来ない。 そして引き続き、色々調べてみる。 Insider's Computer Dictionary [ECCメモリ](@IT) 64ビットの誤り訂正の場合、8ビット必要になる。

| 64ビットのデータと、誤り訂正のための8ビット |

|---|

|

もし、64ビットの中で、1ビットの誤りがあっても 誤り訂正符号によって訂正できるというのだ。

| 1ビットの誤りなら訂正できる |

|---|

|

|

メモリから取り出した64ビットのデータのうち 1ビットの誤りなら訂正できるのだ。 |

そのためECCメモリには以下の図のように、誤り訂正の8ビットを格納する メモリチップが余分についているというのだ。

| ECC付メモリは8ビット分、余分にチップがついている |

|---|

|

|

ECC付メモリは、誤り訂正符号の8ビット分を格納するための メモリチップが余分についているのだ。 |

実際、ECC付メモリを見てみる。 幸い、実験用サーバーがECC付メモリを使っていたので実物が見る事ができた。

| ECC付のメモリの表面 |

|---|

|

| 裏面 |

|

|

メモリチップが4ビットのチップなので表と裏で18個ある ECC無しは16個なので、8ビット分、チップが多くなる。 |

ところで、ECCによる誤り検出訂正は ハミング符号 を使っているのだ。パリティ

ハミング符号を調べる前に、パリティの話を知る必要があった。 そこで、まずはパリティを調べてみる事にした。 パリティとは以下の意味がある。

| パリティ(Parity)の意味 |

|---|

| 同類、一致、偶奇性など |

そこから派生して、誤り検出の意味に使われたりする。

ところで古いメモリの誤り検出にはパリティが使われた。

Fast Page時代のメモリ

なのだ。

と書いても、実は、その頃は私はパソコンを触っていないので

どんな時代だったのか、見当すらつかない。

その後、EDO DRAMの時代からは誤り訂正符号のECCになったようだ。

| パリティ付メモリの時代とは |

|---|

|

実は、調べていくと、SDRAMのPC100の仕様に パリティの有無が書いてあった。 しかし、EDO DRAMでは、そんな物は見当たらない。 調べても、わからなかったのだが、buffaloのメモリ価格のサイトで FastPage DRAM時代までがパリティで、それ以降はECCになったようだ。 メモリ価格改定 (buffalo) もし、私が間違えていましたら、ご指摘をお願いします m(--)m |

初期のDRAMメモリで使われたパリティの話をする。

| 8ビットデータの誤り検出に使われた |

|---|

|

|

FastPage時代は、バス幅は32ビットだった。 もっと昔は8ビットだったため、8ビット単位で考える事が多い。 |

誤り符号は、8ビット目の後ろに付ける1ビット符号だ。

| 誤り符号は、8ビット目の後ろに付ける1ビット符号 |

|---|

|

| 本来の8ビットとパリティの1ビット、合計9ビットのデータになる。 |

パリティ符号の算出の仕方は以下の通りだ。

| パリティ符号の算出の仕方 |

|---|

|

| パリティには、偶数パリティと奇数パリティの2種類ある。 |

もし、奇数パリティの場合で、本体のデータに1ヶ所、誤りが発生した場合を見てみる。

| 奇数パリティの場合で、本体のデータに1ヶ所、誤りが発生した時 |

|---|

|

|

奇数パリティは「1」の数が奇数個だが、誤りデータのため 「1」の数が偶数個になっている。「1」の個数が偶数か奇数で 誤りの有無を見ているのだ。 |

当時のメモリは32ビットのバス幅だったため、以下のようになっていた。

| パリティ無しのメモリ |

|---|

|

|

パリティなしのため、メモリのデータビットは32のだ。 だが、誤り検出ができないため。誤りがあっても そのままシステムは、誤ったメモリデータを使っている状態になる。 |

パリティ有のメモリの場合は以下のようになっていた。

| パリティ有りのメモリ |

|---|

|

|

8ビットにつき1ビットのパリティなので、32ビットバス幅の場合 合計4ビットのパリティが付くのだ。 |

パリティには誤り検出機能があるのだが 偶数個のビット誤りが検出できない という問題があった上 誤りがあっても訂正できない だった。 そのため、誤り検出だけでなく、訂正ができるECCにとって代わられたのだ。ECCの仕組み ハミング符号

そこでハミング符号が何かを調べてみる事にした。 だが、次の説明を見て目が点になった。

| ハミング符号に関する事 |

|---|

|

| 知らない単語のため、意味不明の数式に思える。 |

最初で挫折するのは、格好悪い。 そこで、色々、調べてみると、以下のように読みかえる事ができる。

| 読みかえた物 |

|---|

|

| これだと、わかりやすい。 |

そこで、よくハミング符号の例題に使われるハミング(7,4)符号を 見てみる事にした。 ハミング(7,4)符号とは 送りたいビットは4ビット 誤り訂正符号が3ビット 合計7ビットのデータ なのだ。 以下の構造のデータをいうのだ。

| ハミング(7,4)符号 |

|---|

|

ここからハミング符号を使って、誤りを検出する仕組みの説明が

始まるのだ。

だが、いきなり下の式を見せられても

なんで、こんな式になるねん

だった。

| 本体データと誤り訂正符号のビットの関係式 |

|---|

|

| なぜ、こんな式が出てくるのか、全くわからなかった。 |

だが、ここで挫折するわけにはいかない。 そこで、色々、調べ見ると、わかりやすい例が出てきた。

| 円を使った説明 |

|---|

|

|

円を使うと、式では見えてこなかった関係が見えてくる。 上手にグループ化ができているのがわかる。 |

そして、例として、本体データに具体的な値「0」か「1」を代入してみる。

| 本体データに具体的な値「0」か「1」を代入 |

|---|

|

もし、データに誤りがあった場合を考える。

| もしデータに誤りがあった場合 |

|---|

|

| 円Cに誤りはなく、円Aと円Bの成分に誤りがある事がわかる。 |

グループ化している事で、なんとなく

わかった気になった

のだ。

ここからハミング符号で誤り検出・訂正を行なう話になる。

| 式を細工する |

|---|

|

|

「0」になるようにC1とC1、C2とC2、C3とC3の排他的論理和を出している。 なぜ、こんな事をするのかと聞かれても、わからないのだ。 |

そして、この排他的論理和をシンドロームという。

| シンドローム |

|---|

|

|

S1,S2,S3の値をシンドロームと言うのだ。 そして、誤りがなければ、(S1,S2,S3)=(0,0,0)なのだ。 |

上の式を行列式に置き換える事ができる。

| 行列式に置き換える事ができる |

|---|

|

| シンドロームと、送信データ(本体と誤り訂正符号)との関係式が出る。 |

そして、関係式を見やすくするため記号で表す

| 関係式を記号で表す |

|---|

|

次に、行列の転置行列を求める。

20世紀は理系だった私。

だが、21世紀では完全に非理系の事務職の私なので

転置行列を求めるなんて・・・

20世紀以来の出来事

なのだ。

| 転置行列を求める |

|---|

|

|

なぜ転置行列を行なったのか、この時点では理由がわからなかった。 あとで、その理由がわかるのだ。 |

久々に行なった転置行列。とはいえ、意外と昔の事を思い出せた。 そして、転置行列には以下の法則が成り立つのだ。

| 転置行列の法則 |

|---|

|

| 行列の積の転置行列は、個々の行列の転置行列の積になる。 |

検査行列は、任意の本体データ(X1,X2,X3,X4)と、それに対応した 誤り訂正符号の(C1,C2,C3)の7ビットに対して、唯一の物になる。 そのため、どんなデータを送信する時にも使える。 そこで誤り検出方法を見てみる

| 誤り検出法 |

|---|

|

|

送信データ(本体の4ビットと3ビットの誤り訂正符号)が来た時 検査行列との積をとって、シンドロームを求める。 もし、誤りがなければ、シンドロームの(S1,S2,S3)=(0,0,0)になる。 |

もし、1ビットでも誤りがあった場合、シンドロームの(S1,S2,S3)の値が (0,0,0)でなくなるのだ。

| 誤りがあった場合のシンドロームの値 |

|---|

|

|

X1に誤りがあった場合(S1,S2,S3)=(1,0,1)になる。 誤り箇所が別の所だと、(S1,S2,S3)の値の組み合わせが異なる。 そのため、シンドロームの値を見るだけで、誤り箇所がわかる。 そこで、誤り箇所のビットを変更すれば、訂正できるというのだ。 |

ところで、ふと思った。

誤り訂正符号は、どないして算出するねん?

だが、最初の式の部分に戻ってみて気がついた。

| 誤り訂正符号の求め方 |

|---|

|

|

誤り訂正符号のC1は、X1,X2,X3の偶数パリティだと気づく。 他の誤り訂正符号のC2,C3も同様だ。 |

そしてハミング(7,4)符号とは 3つ偶数パリティで検査しとるやん! というのに気づいた。 ところでECCの特徴だが 2ビットの誤りが検出できる のだ。 ただし、2ビットの誤りは検出できても ビット訂正はできない のだ。デゥアルチャンネル

SDRAMのDDRからの機能になる。 直訳すると「2個の経路」になる。 どういう事なのか。 実はメモリの事を調べていたら、この話が見つかったのだ。 知ってなっとく接続規格 DDR SDRAM-DIMM | BUFFALO バッファロー しかも内容は簡単で メモリを2枚差しすれば2倍の速さになる というのだ。

| 2GBのメモリ1枚よりも1GBのメモリ2枚の方が速い |

|---|

|

|

同じメモリを搭載するなら、1枚にするのではなく 2枚に分割した方が、メモリ速度が速くなるというのだ。 |

もちろん、同じ規格で同じ容量で、同じ会社のメモリである事が前提になる。 そんな話・・・ 知らへんかった!! そして会社のパソコンのメモリの挿している状況を見ていった。 すると・・・ 1枚挿しが結構ある だった。

SPD (Serial Presence Detect)

メモリの事を調べていたら、SPDと言う文字を見た。 技術解説 次世代標準メモリの最有力候補「DDR SDRAM」の実像(@IT) メモリの仕組み・構造 | 自作パソコンの作り方解説 パソコンを買ったらメモリをチェック パソコン購入の知識 メモリ自身の情報が格納されているROMだ。 容量・動作周波数などなど。

| メモリのSPD |

|---|

|

| ピンクで囲んだ部分がSPDと呼ばれるROMだ。 |

調べてみると、SPDが登場する以前は、メモリの設定のため はBIOSの設定を触る必要があったという。 だが、今ではBIOSがSPDに格納されているデータを読み込むため BIOSを触る必要がなくなったという。 メモリの情報を格納したSPD。 どんな情報が格納されているのか気になった。 そこで調べてみたら、以下のサイトを発見した。 マビノギハァンタジーライフ/ウェブリブログ CPU-Z というフリーウェアでCPUの速度、メモリの種類などの詳細がわかります CPU-Zという無償ソフトを使えば、SPDの中身が見れる。 早速、供給元からダウンロードした。 CPU-Z CPUID - System & hardware benchmark, monitoring, reporting

| CPU-Zでメモリ情報を見てみた |

|---|

|

| メモリの型式などの情報が表示される。 |

そしてSPDの情報を開いてみた。

| CPU-ZでメモリのSPD情報を見てみた |

|---|

|

| SPDに格納されている情報が表示されている。 |

スタブ対抗

次にノイズ対策のための抵抗がメモリ上にあるというのだ。

スタブ抵抗という物だ。

| メモリのスタブ抵抗 |

|---|

|

|

スタブ抵抗で電流を制御する事で、メモリエラーを防止している。 だが、なぜメモリエラー防止になるのかは、よくわからん。 |

スタブ抵抗。調べていくと、メモリの品質に大きく関わるという。 信頼性の高いメモリーとそうでないメモリーの見分け方 他にも見ていくと バルク品の中にはスタブ抵抗を外す物もある ところで、「スタブ」という言葉がある。 だが、どういう意味がわからないので調べてみると Stub (切り株・枝) という意味なのだ。 枝わかれしているのか。

| スタブ(Stub)とは |

|---|

|

| 電子回路では主要線があり、支線にあたる部分をスタブという。 |

調べていくうちに、サイトを発見した。 インテグリティな技術コラム(7) ―― スタブの反射はSSTLで回避 メモリでいうスタブとは図にすると、以下の事だという。

| メモリでいうスタブとは |

|---|

|

| ここでのスタブとはバス線から延びている支線の事を差す。 |

だが、この先を読もうとしても電気工学の知識がないので

全く、わからへん!!

だった。

ただし、2頁目にある波形を見ると、スタブ抵抗によって

メモリの電位差の違いが安定した形になっているのがわかる。

これで、さっさと逃げようと思った。

だが、そんな事で、許してくれそうもない読者がいるので

色々、調べていった。

すると以下のサイトで驚く事が書いていた。

測定器玉手箱 計測に関する知識 | 計測器、パソコンレンタルのオリックス・レンテック

高周波の場合、T字路でスタブに信号波が入り、その反射派が問題になるという。

図で説明すると以下のようになる。

| スタブに信号波が入る問題 |

|---|

|

|

家庭用電気では全く問題にならないのでピンと来ないが 高周波だと、スタブに信号波が入り、その反射波が問題なったりする。 電話回線やADSL回線でも同じ問題があるようだ。 各家庭や事務所へ引き込む線をスタブと考える事ができ 反射波などの問題が発生する。それが信号減衰の原因になるようだ。 |

そして、高周波になると、配線自体を回路の一部と考え、

インピーダンスを考慮しなくてはならないというのだ。

高周波おそるべし!

と思った。

| 高周波信号の場合、配線自体を回路と考える必要がある。 |

|---|

|

| 配線のインピーダンスを「Z」と考えてみる。 |

そこで、もう一度、以下のサイトを見てみる事にした。 インテグリティな技術コラム(7) ―― スタブの反射はSSTLで回避|Tech Village (テックビレッジ) / CQ出版株式会社 スタブの先端は100%反射すると考える。

| バスを通った信号の反射波がT字路で反射する割合 |

|---|

|

|

反射波の33%がT字路で反射されてしまう。 スタブ内に信号が残りのが問題になる。 |

ところで・・・

なんで反射率が33%やねん?

と思った。

そこで調べてみると、反射係数の求め方のサイトを発見した。

反射係数

| インピーダンスが異なる配線が接続している場合 |

|---|

|

| 配線の境界面を境に、両側にインピーダンスが異なる配線を考える。 |

この時の反射係数は以下のように求める。

| 反射係数(反射率)の求め方 |

|---|

|

| 電圧の反射の割合。電流の反射の割合を考える。 |

以下の数式が成り立つ。

| 電圧と電流の関係式 |

|---|

|

|

ここでは電圧の反射率を算出する式を求める。 それが反射係数となるのだ。 |

反射係数の算出方法がわかった所で、以下の図に話を戻す。

| スタブに入った信号が先端で100%反射される |

|---|

|

| スタブに入った信号が先端で100%反射される。 |

反射波がT字路で反射される割合は以下のようになる。

| 反射波がT字路で反射される割合 |

|---|

|

|

T字路で本線の両側に流れると考えた場合、インピーダンスは Zの半分と考える事ができる。 |

そのためスタブに入った信号がT字路で反射する割合は33%になる。

| スタブに入った信号がT字路で反射する割合は33% |

|---|

|

| 計算式を当てはめると、反射係数(反射率)が33%になる。 |

そこでスタブ部分に抵抗をつけて、スタブ部分に入った信号が T字路で反射せずに本線に戻す事を行なう。

| スタブ抵抗をつけて反射をなくす |

|---|

|

|

スタブ抵抗を入れる事で、スタブに侵入した信号が スタブに留まらずに、本線に流れてくれるのだ。 |

スタブ抵抗には、もう1つ役目がある。 透過率を高める役割だ。

| スタブ抵抗により透過率が上がる |

|---|

|

|

本線を流れる信号が、T字路でもまっすぐ伝わる率は スタブ抵抗がないと33%だったが、スタブ抵抗を入れる事で 37.5%になる。信号の透過率が上がっているのだ そしてT字路で、本線の反対側に反射する割合が33%から25%に減る。 |

こんな事まで考慮されていたとは知らなかった。 バルク品の安いメモリの場合、スタブ抵抗がない場合がある。 その場合、信号の減衰や信号の波形の乱れで、正常に動きにくくなる 問題が潜んでいる事がうかがえる。 高周波回路を組むようになれば、避けては通れない話になる。 切り欠き メモリを見ると、差し込み部分に凹んだ部分がある。 メモリの説明を見ると「切り欠き」というのだ 読み方がわからへん なのだ。 調べてみると「きりかき」と読むのだ。

| メモリの切り欠き(誤装着防止) |

|---|

|

|

誤装着を防止するため、規格ごとに切り欠きの位置を変えている。 規格の違うメモリを差し込みたくても、差し込めないようになっている |

確かに、違う型式のメモリを差そうとしても、差し込めない体験があった。 だが、単なる型式の違いであって、その先は考えなかった。 誤装着防止のために、意図的に、切り欠きがあるのは知らなかった。

メモリの仕組み

メモリの仕組み。どうやって「0」や「1」のビット情報を記録しているのか。 電気的な記録なので 電源を切ったらデータが消滅 という事だけ知っている。 そこで出てくるのが、SRAMとDRAMの違いだ。

| SRAMとDRAMの違い | |

|---|---|

| SRAM | 高速でやりとり可能。 だが、高価なため、主記憶装置(メモリ)には使われず CPUのキャッシュメモリになっている。 |

| DRAM |

低速処理だが、安価で大容量が可能。 パソコンのメモリに使われている。 |

このぐらいしか違いはわからない。 そこで、まずは、DRAMから調べてみる事にした。

DRAMメモリの仕組み

パソコンに使われるメモリの事をDRAMと言うのだが 一体、DRAMとは何か。 Dynamic Randam Access Memory の略だ。 「動的で、任意のアドレスに読み書きできる記憶媒体」なのだが 直訳すると、意味不明になる。 コンデンサーには電気を貯める性質がある。 それを活用したのがDRAMで、電気が空の状態を「0」とし 充電している状態を「1」としている。

| コンデンサー内の電気で「0」「1」を決める |

|---|

|

コンデンサーの充電機能については、詳しくは「システム奮闘記:その98」 (電気回路入門)をご覧ください。 そしてトランジスタは、メモリにおいて、スイッチの役目を果たす。 充電と放電は以下の図のような方法で行なっているのだ。

| コンデンサーへの充電 |

|---|

|

|

「1」の場合、充電なので電流を流す。 MOSトランジスタと呼ばれる物に電圧をかけると スイッチの役目を行ない、電気が充電される。 電圧をかけるのを止めると電気が充電が止まる。 |

そしてメモリの中身を読み出すのは、コンデンサーからの放電だ。

| コンデンサーの放電の様子 |

|---|

|

|

放電の際、MOSトランジスタと呼ばれる物に電圧をかけると コンデンサーに溜っていた電気が流れる。放電される。 電気がある事で「1」と判断される。 |

これでDRAMの仕組みを説明したと言いたいが、そんな手抜きをすると

キチンと書け!

とお叱りを受ける。

それに、なぜトランジスタがスイッチになるのかの説明にもなっていない。

さて、トランジスタの説明を書かねばならなくなった。

だが、その前に半導体とダイオードの話に、少し触れる必要がある。

| 正直な事を書きます |

|---|

|

DRAMの説明の最初の部分で、MOSトランジスタが スイッチの役目を果たすと書きました。 実際には、その時点ではMOSトランジスタの事は知りませんでした。 バイポラードトランジスタとばかり思っていました。 |

半導体とは N形半導体とP形半導体

電気を流すのは導体。電気を流さない物は絶縁体という。 その中間辺りの物質を半導体という。そのまんまだ。 シリコン、ゲルマニウム、ヒ素、スズ などが半導体の代表だ。 高校の化学で習ったボーアの原子核モデルで説明してみる。

| 水素原子 |

|---|

| 原子核の周りを電子が回っている。 |

高校時代、化学記号を覚える際、メンデレーエフの周期表を思い出す。 水素(H)の次は、ヘリウム(He)、リチウム(Li)、ベリリウム(Be)、ほう素(B)、 炭素(C)という順番だ。 電子を6個もった原子は炭素(C)になる。

| 炭素原子 |

|---|

|

ボーアの原子核モデルの場合、内側はK殻と呼ばれる 電子2個が入る事ができる軌道がある。 その外側はL殻と呼ばれる軌道があり8個、電子が入る事ができる。 その外側はM殻で、電子が18個入る事ができる。 |

軌道と電子が入る個数を表にしてみた。

| 殻と電子の個数 | |

|---|---|

| 軌道名 | 電子の個数 |

| K殻 | 2 |

| L殻 | 8 |

| M殻 | 18 |

| N殻 | 32 |

水素と炭素の場合のボーアの原子核モデルを図にしたが

他の原子まで描くとめんどくさい。以下のサイトをご覧ください。

楽しい高校化学

この化学のサイトを見て、ふと思った。

今の高校化学は、s軌道,p軌道を教えているのか!

s軌道、p軌道とは電子の軌道を、より忠実に描いたモデルだ。

ボーアモデルだと、円形だが、s軌道は円形で、p軌道は楕円になる。

| s軌道、p軌道を使った表現した窒素原子 |

|---|

|

窒素原子は電子を7個持っている。 一番内側の1s軌道に2個。そして二番目の2s軌道に2個。 そして2p軌道に、3つの電子が配分されている。 あくまでも軌道モデルだ。電子の軌道について知りたい方は 頑張って量子力学を勉強してください! |

ところで、世の中、物質は原子単体だけでは存在しにくい。 複数個結合した分子という形で存在する。 水素原子と水素分子について見てみる。

| 水素原子が結合して水素分子になる |

|---|

|

水素原子の周囲を電子1個回る。この軌道は2個あって安定する。 そのため水素原子同士が結合し、あたかも2個電子を持った形にして 安定しようとする。これを共有結合と呼ぶ。 |

では炭素(C)の場合はどうなるのか。 炭素は6個電子を持っている。

| 炭素原子を考えてみる |

|---|

|

K殻にあたる1s軌道は2個ある。 L殻にあたる2s軌道は2個、p軌道は2個ある。 |

こんな場合はどうなるのか?

sp混成軌道に変身

なのだ。

| 炭素原子と電子軌道 (sp混成軌道) |

|---|

| L殻にあたるsp混成軌道が4つあり、それぞれ電子を1個持った形になる。 |

炭素原子は4方向に結合の手ができる事を意味する。

| 炭素原子同士が共有結合をする |

|---|

|

炭素原子が、4方向に結合の手を伸ばしあって、それぞれの電子を共有し 共有結合が行なわれる。 |

ただ、K殻の2個の電子を表記しても意味がないので 以下のように共有結合に関する電子のみ表記をする場合が多い

| 炭素原子の共有結合 |

|---|

| この方が、すっきりして見やすくなる。 |

電子軌道については、以下のサイトは私が書くよりわかりやすい。 役に立つ薬の情報 電子軌道 リンクを張りまくっているので、突貫工事の化学の勉強と 思われそうだが・・・ この程度なら知っている (^^) のだ。 たまには、見栄を張らない状態で「知っている」と書いてみるのだ。半導体

半導体には結合の手が4本あるシリコン(Si)やゲルマニウム(Ge)が使われる。 ここでは、本でよく使われるゲルマニウムで説明してみる。

| ゲルマニウム(Ge)の結晶格子(共有結合) |

|---|

| 炭素同様、4本の結合の手があるので、それぞれ共有結合を行なう。 |

電気が流れるのは、電子が流れている状態を差す。

ところで、上図のような電子が共有結合で使われ

自由電子と呼ばれる物がなければ電気が流れない。

ただ、ゲルマニウムの結合の場合、緩やかな結合のため

熱を加えると、共有結合に使われている電子が自由電子になり

電気が流れるようになる。

銅やアルミなどの金属は、温度が上がると電気が流れにくくなる。

金属抵抗率と温度

だが、シリコンやゲルマニウムは温度を上げると、電気が流れやすくなる。

N形半導体

Geの規則正しい結晶格子の中に、不純物を少し混ぜる。

まずは不純物をアンチモン(Sb)にした場合を見てみる

| アンチモン(Sb)と結合の手 |

|---|

| アンチモン(Sb)の場合、5本の結合の手がある。 |

そのためGeの結晶の中に、Sbを入れたら、次のようになる。

| Ge結晶の中にSbを入れた様子 |

|---|

|

アンチモン(Sb)は結合の手が5つある。 だが、ゲルマニウム(Ge)は結合の手が4つしかないため 1個余分になる。茶色の部分だ。 要するに電子が余る事になる。 電子が余分にできた不純物が入った半導体をN形半導体と呼ぶ |

自由電子がある状態だ。 N形半導体に電気を流すと、電子の流れが生まれる。

| N形半導体に電気を流す |

|---|

|

電気が流れる際、電圧がかかるため、不純物のアンチモン(Sb)が持つ 余分な電子が移動して、電気が流れる |

P形半導体

次に、ガリウム(Ga)を不純物として混ぜた場合を見てみる

Ga原子を見てみる

| ガリウム(Ga)原子 |

|---|

| Gaは結合の手が3本しかない。 |

Geの結晶体に、Ga不純物の入れた場合を見てみる。

| Geの結晶体にGaを混ぜた場合 |

|---|

|

結合の手が3本しかないため、電子が不足している部分ができる。 その部分を「正孔」と呼ぶ。「孔」は「穴」という意味がある。 「正の電荷を持つ穴」みたいない存在なので「正孔」と呼ぶ。 |

P形半導体に電気を流すと、正孔が動き出す。

| P形半導体に電気を流す |

|---|

| 電気を流すと、電圧に押された形で正孔が移動する。 |

電子が流れる様子は描きやすいが、正孔が動く様子は 頭の中で描きにくいし、ピンと来ない。 だが、次のように見れば、わかりやすい。

| 電子動きと正孔の移動を見比べる |

|---|

|

実際は電子が移動する事で、電子欠損部分が移動している形になる。 電子欠損部分が正孔なので、あたかも正孔が移動しているように見えるのだ。 |

私なりには「なるほど」と思う説明だ。

何やら第三者の感想に思える。そのわけは・・・

WikiPediaの「正孔」の図のパクリ

なのだ。

見栄を張って自分が思いついたと書いても、見破られる。

それだったら、最初からパクリと認めれば良いのだ (^^)

そして、もう1度、N形半導体に電気を流した場合を見てみる。

| P形半導体に電気を流す |

|---|

|

電圧をかけると、電子が電位の高い所へ移動する。 そのため、電子の欠損部分(正孔)が移動するように見えるのだ。 |

PN接合ダイオード

トランジスタの話を書く前にダイオードの説明が必要になる。 ダイオードとは電気を一報方向にしか通さない電子素子だ、 ところでダイオードはP形半導体とN形半導体を合体させた物だ。

| PN結合ダイオード |

|---|

| P形の部分には過剰に正孔があり、N形の部分には過剰に電子がある。 |

さて、これを順方向と呼ばれる電気が流れる方向に 電気を流してみると、以下の現象が起こる。

| 順方向に電気を流す |

|---|

|

正孔と電子がPN接合面に向かって動いている。 正孔の動きは、電子欠損部分なので、実際には 反対方向に電子が流れているのだ。 |

順方向だと電気が流れる。 だが、反対方向に電気を流そうとすると、電気は流れない。 以下の現象が起こっているからだ。

| 反対方向に電気を流そうとした場合 |

|---|

|

P形の正孔・N形の電子共に接合面とは反対方向に動く。 P形側の接合面近くでは正孔がなくなる。 そしてN形側の接合面付近では電子がなくなる。 接合周辺が空乏層と呼ばれる絶縁体ができ、電気が流れなくなる。 |

そのためダイオードに逆方向に電気を流そうとしても流れないため 電気を一方しか流さない電子素子といわれる。

| ダイオード |

|---|

|

だが、逆方向でも、ある一定以上の電圧をかけると電気が流れる。

| ダイオードの電気的特性 |

|---|

|

反対方向に、ある一定以上の電圧をかけると、急激に電気が流れる。 カスケード現象の場合もあれば、トンネル効果の場合もある。 |

これを応用したのがツェナーダイオードだ。

| ツェナーダイオード |

|---|

|

|

反対方向に、ある一定以上の電圧をかけると、急激に電気が流れる。 カスケード現象の場合もあれば、トンネル効果の場合もある。 これを使って、整流器のリップル成文を取り除いたり 雷サージ対策の電源タップに使われたりしている。 |

ツェナーダイオードの話は「システム奮闘記:その98」をご覧ください。

電気回路入門

トランジスタ

ようやくトランジスタの話になる。

トランジスタはスイッチに役目を果たす。

なぜ、スイッチになるのかを書いてみる。

トランジスタには、N形とP形の半導体を組み合わせた

NPN形トランジスタとPNP形トランジスタがある。

| NPN形接合トランジスタ |

|---|

| P形半導体の両側を、N形半導体で、はさんだ形になる。 |

| PNP形接合トランジスタ |

|---|

| N形半導体の両側を、P形半導体で、はさんだ形になる。 |

PNP形接合トランジスタで見てみる事にした。

| PNP形接合トランジスタ |

|---|

|

ベースとコミッタ間に電流を流してみようとすると ダイオードで反対方向に電気を流そうとする現象と同じ事が起こり 全く電流が流れない。 |

そこでベースとエミッタ間も電気を流してみる。

| ベースとエミッタ間も電気を流してみる |

|---|

| 回路図になる。 |

| ベースとエミッタ間も電気を流してみる |

|---|

|

正孔はエミッタ側に引き寄せられ、空乏層はできない。 エミッタ側のN形半導体内の電子もP形に引き寄せられる。 エミッタ側の余分な電子でP形半導体を飛び越え コミッタ側のN形半導体に流れる。 |

上図のような現象で、電流が流れるのだ。 上図の回路を、以下のように組む事ができる。

| エミッタ接地回路 |

|---|

| エミッタ側を共通端子(アース)にする回路だ。 |

この場合もコミッタ・エミッタ間で電気が流れる

| コミッタ・エミッタ間で電気が流れる |

|---|

|

エミッタ・ベース間に電流を流すと、それにつられて エミッタ・コミッタ間も電流が流れる。 トランジスタが増幅器だけでなく、スイッチと呼ばれる理由だ。 |

トランジスタの話が見えてきた。 だが、ここまで取り上げたNPN形(PNP形)トランジスタは バイポラードトランジスタ と呼ばれる物だ。 DRAMメモリに使われるのは、MOSトランジスタだ。 同じトランジスタでも内部構造が異なる。 折角、ここまで絵を描いたりして頑張ったのだが 討ち死にしてしまった気分だ・・・。FETトランジスタ (電界効果トランジスタ)

DRAMメモリに使われるトランジスタがバイポラードではなく 他のトランジスタだったため、別のトランジスタの概略の勉強を しなければならなくなった。 MOSトランジスタだとわかり、MOSトランジスタを調べようとしたら MOSはFETの一種 が目に飛び込んできた。 そこでFETトランジスタを調べる事にした。 FETトランジスタ(ジャンクションFET)の概略と動作原理、特性 FETは Field effect transistor の略で、日本語にすると 電界効果トランジスタ になる。 そしてN形半導体、P形半導体の知識が、そのまま使える。 バイポラードトランジスタを勉強したのが無駄ではなかった。 FETトランジスタには、NチャンネルとPチャンネルがある。 Nチャンネルを見てみる事にした。

| FET 電界効果トランジスタの仕組み |

|---|

|

|

NチャンネルのFETトランジスタだ。 ゲート(水門)がある。なぜ、水門なのかは少し後で説明します。 そしてソースとドレインがある。よく見ると、同じように見える。 実は区別はないのだ。配線の際、電圧が高い側をドレインと呼び 電圧の低い側をソース呼ぶ。便宜的に分けているのだ。 ソース(Source)は「源」で、ドレイン(drain)は「排水口」だ。 |

ドレインとソースをつなげてみると、電気が流れる。

| ドレインとソースをつなげてみると、電気が流れる |

|---|

|

| N形半導体なので電子が流れができ、電気が流れる。 |

ここでゲート(Gate:水門)の登場だ。

| ゲートに電圧をかける |

|---|

|

|

ゲートに電圧をかける。 するとダイオードで逆方向に接続した場合と同じ現象が起こる。 |

そして空乏層が生まれる。

| 空乏層が生まれる |

|---|

|

|

空乏層ができ、電子が通るのを妨げてる。 電気が流れにくくなっているのだ。 |

そして、ついに電気が流れなくなる。

| 電気が流れなくなる |

|---|

|

|

大きくなった空乏層が電子の流れを止めてしまう。 結果、電気が流れなくなる。 ゲートに電圧をかける事で、水の流れを堰き止めるようなので ゲート(水門)と呼ばれる理由だ。 |

FET(電界効果トランジスタ)と呼ばれるのも 電圧をかける(電界の効果)を使っているためだ。MOSトランジスタ

ようやくMOSトランジスタの話になった。 MOSを知らねば、DRAMのトランジスタの振る舞いが理解できない。 そこで仕組みを調べてみる事にした。 トランジスターの仕組み MOSFET がスイッチとして動作する仕組み (インテル) 情報通信工学科 電子回路 I(東京工科大学) MOS FET MOSの略は Metal Oxide Semiconductor という意味だ。 日本語にすると 金属酸化膜半導体 なのだ。 わかったような、わからんような言葉だ。 そんな時は、納得できていない証拠なのだ。 電界効果トランジスタの一種なので MOSFET と表記する事もある。 FETと同様、MOSにもNチャンネルとPチャンネルがある。 まずはNチャンネルを見てみる。

| MOSFETの中身 Nチャンネルの場合 |

|---|

|

|

ゲートがある。FETと同様、水門の役割を果たす。 N形、P形半導体との接触部分には電気を通さない酸化膜を張り その上に金属をのせている。 これがMOS(金属酸化膜半導体)と言われる理由だ。 ソースとドレインだが、これも便宜的な物だ。 配線の際、電圧が高い側をドレイン。低い側をソースと呼ぶだけだ。 FETにはなかった物として、MOSにはバックゲートがある。 だが、MOSトランジスタの動きを見る際には無視して良いので 省略している場合が多い。このシステム奮闘記でも省略する事にした。 |

さて、ソースとドレインを結んでも電気は流れない。

| ソースとドレインを結んでも電気は流れない |

|---|

|

|

何もしていない状態だと電気は流れない。 ところでバックゲートを省略できるので、省略した図を描いた。 ちなみに記号も、簡略化した物があるのだ。 |

次にゲートに電圧をかけてみる。

| ゲートに電圧をかけてみる |

|---|

|

すると以下の現象が起こる。

| ゲートに電圧をかけるとN形半導体内の電子が寄ってくる |

|---|

|

|

ゲートとP半導体の間は電気を流さないが、金属内の電子が奪われるため 金属は正の電荷を帯びた状態になる。そして電圧がかかった状態になる。 まるでコンデンサーのようだ。 その時、N形半島体内では、電界に引き寄せられた電子が ゲート方面に集まってくる。 |

あつまった電子によって、擬似的にN形の状態が形成される。

| 電子の通り道ができる |

|---|

|

|

電子が集まる事で、まるでN形の状態が形成される。 この部分をNチャンネルと呼ぶ。 チャンネル(channel)とは「流れ、川」という意味がある。 N形をした経路という意味だ。 |

そしてNチャンネルが形成される事で、電気が流れるようになる。

| 電気が流れるようになる。 |

|---|

|

|

Nチャンネルを使って、電気が流れるようになる。 まさに、Nチャンネルのゲートは、電圧をかける事で 水を流すための水門という感じになる。 |

これでトランジスタがスイッチになる事が説明できた。 次にPチャンネルMOSトランジスタ(P-MOS)についても触れてみる。

| MOSFETの中身 Pチャンネルの場合 |

|---|

|

|

NチャンネルのMOSトランジスタ同様にゲートがある。 文字通り(Gate:水門)の役割を果たす。 N形、P形半導体との接触部分には電気を通さない酸化膜を張り その上に金属をのせている。 これがMOS(金属酸化膜半導体)と言われる理由だ。 ソースとドレインだが、これも便宜的な物だ。 だが、配線の際、Nチャンネル(N-MOS)と異なり 電圧が高い側をソース。低い側をドレインと呼ぶのだ。 P-MOSトランジスタにもバックゲートがある。 だが、MOSトランジスタの動きを見る際には無視して良いので 省略している場合が多い。このシステム奮闘記でも省略する事にした。 |

さて、ソースとドレインを結んでも電気は流れない。

| ソースとドレインを結んでも電気は流れない |

|---|

|

|

何もしていない状態だと電気は流れない。 ところでバックゲートを省略できるので、省略した図を描いた。 ちなみに記号も、簡略化した物があるのだ。 |

次にゲート部分の電圧を下げてみる

| ゲートに電圧を下げてみる |

|---|

|

すると以下の現象が起こる。

| ゲートの電圧を下げるとP形半導体内の正孔が寄ってくる |

|---|

|

|

絶縁体があるため、ゲートからはN形半導体の間は電気を流さないが 金属内の電子が溜っていくため、金属は負の電荷を帯びた状態になる。 そして反対側に電圧がかかった状態になる。 まるでコンデンサーのようだ。 その時、P形半島体内では、電界によりゲート付近の電子がゲートから遠い所へ 移動していく。正孔がゲート付近によってくると見ても良い。< |

あつまった正孔によって、擬似的にP形の状態が形成される。

| 電子の通り道ができる |

|---|

|

|

正孔が集まる事で、まるでP形の状態が形成される。 この部分をPチャンネルと呼ぶ。 チャンネル(channel)とは「流れ、川」という意味がある。 P形をした経路という意味だ。 |

そしてPチャンネルが形成される事で、電気が流れるようになる。

| 電気が流れるようになる。 |

|---|

|

|

Pチャンネルを使って、電気が流れるようになる。 まさに、Pチャンネルのゲートは、電圧をかける事で 水を流すための水門という感じになる。 |

N-MOSとP-MOSはスイッチに役割を果たすが、2つの違いを表にしてみる。

| 2つの違い | |

|---|---|

| N-MOS | ゲートの電位を上げる事で電気を流す |

| P-MOS | ゲートの電位を下げる事で電気を流す。 よく使われるのはゲートの電位を「0」にする事で 電気を流すスイッチにしている。 |

DRAMの内部の概略

MOSトランジスタの説明ができた所で、DRAMの概略を説明します。 4ビットのメモリ空間があるとする。

| 4ビットのメモリ空間 |

|---|

|

| 4ビット(16通り)のメモリ空間がある。 |

16通り全てを表した空間を表現するのだが 1次元と、2次元(格子状)の両方で表現できる。

| 4ビットのメモリ空間を1次元と2次元で表現 |

|---|

|

|

視覚的には1次元の方がわかりやすい。 だが、2次元にするのはDRAMの概略を知る上で大事になるからだ。 |

DRAMの内部の配線も、アドレスを上位と下位でわけている。 理由は、アドレス線を減らすのが目的だ。と受け売りを書く (^^) 詳細は後述しています。 実際に、DRAMの概略図を、4ビットメモリの場合で見てみる。

| DRAMメモリの構造 アドレスの上位と下位を縦と横にわける |

|---|

|

|

上位2ビットと下位2ビットで格子状のアドレス表現をする。 メモリアクセスの際、アドレスの上位部分は行の並びの線を使い 下位部分は列の並びの線を使う。 |

言葉で書いても説明しにくいので、図を使って説明してみる。

| DRAMメモリの構造 アドレス「0101」の中身の値を表すコンデンサーは、どれになるのか |

|---|

|

| 赤く囲んだ部分が、該当の値を格納するコンデンサーだ。 |

そこでもし、4ビットメモリのアドレス内にある値を 以下の表の通りだったとする。

| 4ビットメモリのアドレスと中身の値 | |

|---|---|

| アドレス | 値 |

| 0000 | 0 |

| 0001 | 0 |

| 0010 | 0 |

| 0011 | 1 |

| 0100 | 1 |

| 0101 | 0 |

| 0110 | 1 |

| 0111 | 0 |

| 1000 | 0 |

| 1001 | 1 |

| 1010 | 0 |

| 1011 | 0 |

| 1100 | 0 |

| 1101 | 0 |

| 1110 | 1 |

| 1111 | 0 |

2次元(格子状)で表現してみる。

| 4ビットメモリのアドレスと中身の値 | |||||

|---|---|---|---|---|---|

| 下位アドレス | |||||

| 00 | 01 | 10 | 11 | ||

| 上位 アドレス | 00 | 0 | 0 | 0 | 1 |

| 01 | 1 | 0 | 1 | 0 | |

| 10 | 0 | 1 | 0 | 0 | |

| 11 | 0 | 0 | 1 | 0 | |

この時、DRAMメモリ内のコンデンサーの様子は以下のようになっている。

| メモリ内のコンデンサーの様子 |

|---|

|

|

「0」の値が格納された場所(アドレス)に該当するコンデンサーは 電気が溜っていない。 「1」の値が格納された場所(アドレス)に該当するコンデンサーは 電気が溜っている |

あるアドレスに格納している値を取り出したい。

アドレス「1001」の値を取り出したい

とした場合、メモリ内では以下の仕組みで値を取り出す。

| 指定したアドレスに格納された値を取り出す仕組み |

|---|

|

|

まず「1001」の上位アドレス「10」に該当する線に電圧をかける。 赤い部分になる。 |

すると、MOSトランジスタは以下の振る舞いを行なう。

| MOSトランジスタの振る舞い |

|---|

|

|

MOSトランジスタのゲートに電圧がかかる事で トランジスタのドレインからソースへ電気が流れる状態になる そのためコンデンサーが放電される仕組みなのだ。 |

以下の図のようにアドレス「1001」の値が取り出せるのだ。

| アドレス「1001」の値が取り出せた様子 |

|---|

|

|

上位アドレス「10」に該当する線に電圧をかける事で 「1001」の値に該当するコンデンサーから電気が放電される事で 「1」という値が取り出せた。 |

でも、これで終わりではない。 メモリの値を記録するコンデンサーから電気が放出されたため 元に戻す必要がある。 その作業を「プリチャージ」と呼ぶ。

| プリチャージの様子 |

|---|

|

| 「1」の情報を保管していたコンデンサーを充電する。 |

これで完了だ。DRAMの動作の仕組み

ところでメモリが格子状になった理由。 1KビットのDRAMメモリの時代に遡るようだ。 今さら聞けないメモリーの基礎知識 FP BEDO DRAM編(ASCII.JP) 「Intel 1103」のメモリが出たのは1970年。 私より年上 なのだ。 Intel 1103 PCのスピードを左右するメモリーの進化を振り返る(ASCII.JP) DRAMの歴史の古さを感じた。 1Kビットの場合、2の10乗だ。「0」「1」を表現する信号線が10本必要だ。 だが、上位アドレスと下位アドレスを2回にわけると5本で済む。 以下のような仕組みだ。

| DRAMの仕組み (初期の頃) |

|---|

|

|

DRAMが出た頃のメモリの仕組みの概略だ。 センスアンプという増幅装置がある。 ここを通じて、メモリの読み書きを行なう。 |

データの読み込み

データの読み込みの場合、以下のような動作になる。

| データの読み込み開始 |

|---|

|

|

まずはRAS線が「High」から「Low」に変わる。 アドレス指定の際、まずは行アドレスから行なうため 行アドレスの指定の目印として、RAS線の信号を 「High」から「Low」に変えるのだ。 そして信号線からやってきたアドレス情報を 行ラッチに保管する。 |

ところで・・・

ラッチって何やねん?

調べてみると、1ビットの情報を保管する回路なのだ。

コンデンサーではなくトランジスタで記憶させる回路なのだが

この時点では、そんな事を知らなかった。

ラッチについては、後述しています。

そして該当の行アドレスの所のコンデンサーに電気を送る。

| 該当の行アドレスの所のコンデンサーに電気を送る |

|---|

|

|

その結果、コンデンサーから電気が放出される。 1行分のデータがまるごと、センスアンプに送られ、保管される。 |

だが、これでは上位部分のアドレス特定しただけだ。 1行分の丸ごとのデータを取り出したに過ぎない。 そこで次に、下位部分のアドレスの指定して、1行分のデータの中から 該当のデータを取り出さす必要がある。

| CAS線がHightからLowに変わる |

|---|

|

|

信号線から下位部分のアドレスが送られる。 列アドレスである事を知らせるため、CAS線の信号が HighからLowに変わる。 センスアンプに「読み込み中」を伝えるため 書き込み制御線が「High」になる。 信号線から来たアドレスは列ラッチに保管される。 |

そして列ラッチから列デコードにアドレス情報が伝わる。

| 列ラッチから列デコードにアドレス情報が伝わる |

|---|

|

| 列デコードに伝わった後、センスアップに送られる。 |

センスアンプに送られたコンデンサーの情報と 列デコードから送られた情報と照らし合わせて 該当のデータを見出す。

| メモリの情報を取り出し |

|---|

|

|

指定されたアドレスの情報を出力する。 これでメモリの読み込みの完了だ。 |

読み込みの際、「1」の記録をしていたコンデンサーから 電気を放出したため、それを充電する必要がある。 充電作業をプリチャージという。 この時、RAS線、CAS線の信号を「High」に戻す。

| プリチャージ |

|---|

|

そして最初の状態に戻る。 この時、書き込み制御線は「High」から任意の値になる。

| 最初の状態に戻る |

|---|

|

これでメモリのデータの読み出しの作業は完了だ。 ところでメモリから読み出しはクロックでタイミングをとっている。 その様子は以下の図のようになる。

| データ読み出しのタイミング |

|---|

|

|

書き込み制御線が「不定」になっているのは、初期状態の時 特に値を決めていないようだ。そして読み込みの際は「High」になり 書き込みん際は「Low」になる。そのため行アドレスを読み込む際は 特に値が決まっていない状態なので「不定」になっている。 プリチャージの時間だがわからない。 メモリによって異なるため、不明にしておこう。 |

今でこそ、メモリのタイミングを取る際は、マザーボードにある コントローラーからクロック信号を送って、メモリ内の処理の タイミングを取るのだが、当時のメモリは 非同期型 だったので、クロックは存在しなかった。 そのため、上図もクロックは載せていないのだ。 SRAMが高速なのは、このプリチャージがないからだ。 データの書き込み 次にメモリへのデータの書き込みの場合、以下のような動作になる。

| データの書き込み開始 |

|---|

|

|

まずはRAS線が「High」から「Low」に変わる。 アドレス指定の際、まずは行アドレスから行なうため 行アドレスの指定の目印として、RAS線の信号を 「High」から「Low」に変えるのだ。 そして信号線からやってきたアドレス情報を 行ラッチに保管する。(ラッチについては後述しています) |

そして該当の行アドレスの所のコンデンサーに電気を送る。

| 該当の行アドレスの所のコンデンサーに電気を送る |

|---|

|

|

その結果、コンデンサーから電気が放出される。 それがセンスアンプに保管される。 1行ごと、まるごとデータをセンスアンプに送るのだ。 |

だが、これでは上位部分を特定しただけで、下位部分のアドレスの メモリの情報を全てセンスアンプに記録したままだ。 そこで下位部分を特定して、該当のメモリアドレスの値を取り出す必要がある。

| CAS線がHightからLowに変わる |

|---|

|

|

信号線から下位部分のアドレスが送られる。 列アドレスである事を知らせるため、CAS線の信号が HighからLowに変わる。 センスアンプに「書き込み中」を伝えるため 書き込み制御線が「Low」になる。 信号線から来たアドレスは列ラッチに保管される。 |

そして列ラッチから列デコードにアドレス情報が伝わる。

| 列ラッチから列デコードにアドレス情報が伝わる |

|---|

|

| 列デコードに伝わった後、センスアップに送られる。 |

メモリに書き込むデータのアドレスと、センスアンプに送られたデータで 該当のアドレス部分だけを書き換える。

| メモリの情報を書き換え |

|---|

|

|

1行ごとのデータを取り出しているのだが 該当するのは1ヶ所なので、その部分だけ書き換える。 |

そして1行ごと、まとめて充電を行なう。 この時、RAS線、CAS線の信号を「High」に戻す。

| プリチャージ |

|---|

|

そして最初の状態に戻る。 この時、書き込み制御線は「Low」から任意の値になる。

| 最初の状態に戻る |

|---|

|

これでメモリのデータの書き込みの作業は完了だ。 読み込みと同様にクロックでタイミングをとっている。 その様子は以下の図のようになる。

| データ書き込みのタイミング |

|---|

|

|

書き込み制御線が「不定」になっているのは、初期状態の時 特に値を決めていないようだ。そして読み込みの際は「High」になり 書き込みん際は「Low」になる。そのため行アドレスを読み込む際は 特に値が決まっていない状態なので「不定」になっている。 |

リフレッシュ 気分爽快を連想しそうだが、そんな意味ではない。 「1」の情報としてコンデンサーに保管しているのだが 充電時間が短い という問題がある。 そこで 定期的に電気の補充 が必要になる。 どれくらいの割合で行なうのか。 調べてみると、マイクロン社の技術資料に載っていた。 TN-47-16: Designing for High-Density DDR2 Memory - Micron DDR2のメモリの場合、コンデンサーが保持できる時間は 64msにしているため 64msに一度 の割合で、1つの行のコンデンサーのリフレッシュが行なわれている。 だが、行は1つでなく、沢山ある。 64ms間に、全ての行のリフレッシュを行なう必要がある。 資料によれば行数は、16K行(1024×1024×16=16777216行)なので 単純計算すると 64ms ÷ 16777216 = 約3.8μs という短い間隔で、次々とリフレッシュを行なっているのだ。 そんな凄まじい事がメモリ内で行なわれているとは知らなかった。 セルフリフレッシュという機能もある。 セルフリフレッシュとはどのような機能ですか?(IO-DATA) メモリ自身が自分でリフレッシュを行なう事で電力消費を抑えるというが そこまで調べる気力がないのらー! というわけで、勝手に断念してしまう。 DRAMは、プリチャージだけでなく、リフレッシュのため SRAMに比べてメモリの速度が遅い理由がわかったのだ。Fast Page Mode

初期のDRAMメモリの仕組みを知った。 だが、これではメモリの処理が遅いため、1993年頃に Fast Page DRAM が登場した。 次に必要なデータは近くにある という発想だ。 先ほどの初期のDRAMの復習。

| メモリからデータを取り出す方法 |

|---|

|

|

最初に行アドレスを取り出す。 そして該当の列のデータを取り出す。 |

仮りに、次に取り出したいデータが隣にある場合でも 意外と手間がかかる。

| 次に取り出したいデータが隣にある場合 |

|---|

|

|

隣にある場合でも、もう一度、行アドレスのデータを取り出して そこから該当の列のデータを取り出す必要があった。 これでは行アドレスを指定して、データを取り出す時間が無駄になる。 |

そこで以下のように考えたのだ。

| 次に必要なデータは近くにある |

|---|

|

|

連続したデータの場合、次に取り出したいデータは 隣や近くのアドレスにあるはずと考える。 そこで1行のアドレスのデータを取り出した後 同じ行アドレスのデータを順番にとっていくのだ。 それによって、データを取り出す度に、行アドレスの指定と 1行アドレスのデータを丸ごと取りにいく手間と時間が省ける。 |

時系列で処理を見た場合、次のようになる。

| 時系列で処理を見た場合 |

|---|

|

|

行アドレスを読んだ後、連続して列アドレスを読み込むため RASは「High」にしたままにする。 |

EDO DRAM

Fast Page Mode DRAMの次に1995年頃にEDO DRAMが登場した。 だが、あまり普及しなかったようだ。 そのため踏み込んだ事を調べる気が起こらないので 忍法「さっさと逃げる術」 を使いたくなる。 でも、あまり驚く変化はない。 センスアンプとデータ線の間に、一時的に情報を格納する 部分(バッファ)を設けたという話だ。SDRAM登場

現在のパソコンのDRAMに当たる、SDRAMが1996年頃に登場した。 Synchronous DRAM (同期型DRAM) の略だ。 「同期」と書いているからクロックと関係がある。 今さら聞けないメモリーの基礎知識 SDRAM DDR3編(ASCII.JP) EDO DRAMまではクロック信号でタイミングを取っていなかった。 だが、SDRAMからはマザーボードにあるメモリコントローラーから 送られるクロック信号で、タイミングをはかるようになったのだ。 そのため・・・ RAS線、CAS線も不要になった というのだ。

| SDRAMの内部の概略 |

|---|

|

|

クロック信号でタイミングをはかるため、RAS線やCAS線を使って

行アドレス列アドレスのタイミングをを伝える必要がなくなる。 |

時系列で処理の内容は以下の図のようになる。

| SDRAMの処理を時系列で見た場合 |

|---|

|

|

クロック信号で同期をとっている。 (注意点) あくまでも時系列処理を説明するために 行アドレスや列アドレスを伝える時間を 1クロックにしていますが 実際には、1クロックとは限りません。 |

CASレイテンシ (CL値) メモリの性能を見る上で、CL値がある。 CL=2とかCL=3というのは見るのだが どんな値やねん? だった。 だが、SDRAMの話を見ている間に、CLの意味が書いていた。

| CASレイテンシ (CL値)とは |

|---|

|

|

RAS-CAS遅延とは行アドレス信号が出てから 列アドレス信号が出るまでのクロック数を言う。 CASレイテンシは、列アドレス信号が出てから データが読み出されるまでのクロック数をいう。 |

SDRAM DDR

DDRとは、最初の方でも書いたのだが Double Date Rate の略で、データの読み書きが2倍になった物だ。

| DDRでのデータの読み書き |

|---|

|

|

DDRでは、行ラッチ、列ラッチから同時に2個のセル (情報を格納しているコンデンサー群)に接続している。 そのためDDRでは2倍のデータが扱えるようになった。 |

同時に接続しているセルの数が DDR2の場合は4個。なので4倍速 DDR3の場合は8個。なので8倍速 のデータ転送を実現しているのだ。 長い道のりを経て、ようやくDDR、DDR2、DDR3の意味がわかった。

SRAMの仕組み

DRAMの概略がわかった所で、今度はSRAMの概略を見てみる事にした。 SRAMはCPUのキャッシュメモリに使われる。 高速だが、大容量でない上、高価なため、主にキャッシュに使われる。 SRAMとはトランジスタを組み合わせた回路だ。 DRAMはコンデンサーで「0」と「1」を記憶させていたが SRAMではトランジスタに覚えさせる。 ところでSRAMの概略を知るには論理回路の知識が必要になってくる。 そこで論理回路の勉強をする事になった。 そこで以下の本を読む事にした。 「よくわかる最新電子回路の基本と仕組み」(国島保治:秀和システム)論理回路

論理回路には3つの演算回路がある。

| 3つの演算回路 | |

|---|---|

| 1 | 論理和 |

| 2 | 論理積 |

| 3 | 否定回路 |

まずは論理和回路を見てみる

| 論理和回路 (OR回路) |

|---|

|

|

論理和回路の記号と、等価回路の例を見てみた。 並列回路のような物を描いておけば良さそうだ。 「OR回路」と言う場合もある。 |

次に論理積回路を見る。

| 論理積回路 (AND回路) |

|---|

|

|

論理積回路の記号と、等価回路の例を見てみた。 直列回路のような物を描いておけば良さそうだ。 「AND回路」と言う場合もある。 |

次に否定回路だ。

| 否定回路 (NOT回路) |

|---|

|

|

入力した物を否定した結果が出力される。 「NOT回路」と言う場合もある。 |

この回路のわかりやすい例が本に載っていない。

となると・・・

抽象的でわかりにくくなる

という不安を持ってしまう。

次に排他的論理和の回路だ。

| 排他的論理和 (EX-OR回路) |

|---|

|

|

排他的論理和回路の記号だ。 「1+1=0」になるのが、論理和との違いだ。 「EX-OR回路」とも言う。 |

排他的論理和回路だが、他の回路の組み合わせで作れる。

| 他の回路の組み合わせで作れる排他的論理和回路 |

|---|

|

|

論理和回路、論理積回路、否定回路の組み合わせで 排他的論理和回路を組めるのだ。 |

論理演算は難しくないので、問題なくできるのだが・・・ 無味乾燥で退屈 になってくる。 しかも具体例がないだけに だから何やねん? と思って、読み飛ばしたくなる部分だ。 ところでNOR回路、NANA回路という物もある。

| 論理和の否定回路 NOR回路 |

|---|

|

|

論理和を否定した回路と、その記号だ。 「NOR回路」(Not OR)とも言う。 |

次にNAND回路だ。

| 論理積の否定回路 NAND回路 |

|---|

|

|

論理積を否定した回路と、その記号だ。 「NAND」(Not AND)とも言う。 |

でも、この辺りから

全然、具体的な回路じゃないやん!

と言い出したくなった。

そもそもAND回路や、NAND回路などは概念的な物で

具体的な回路なんて、あるのか、疑いたくなった。

だが、本にNOR回路を4つ組み込んだICチップと

NAND回路を4つ組み込んだICチップを載せていた。

| TC4001BのICチップ |

|---|

|

| 4つのNOR回路が入っている。 |

そしてNAND回路を組み込んでいるICチップがある。

| TC4011BのICチップ |

|---|

|

| 4つのNAND回路が入っている。 |

この時、以下の誤解をしてしまった。

NORやNAND回路ならICチップで手に入る

だった。

でも、その誤解のお蔭で、次に進む事ができた。

NOR回路、NAND回路を使った代用回路の話だ。

| 否定回路(NOT回路)の作り方 |

|---|

|

|

NOR回路、NAND回路を使って、NOT回路が作れる。 NOR回路、NAND回路を代用できるのだ。 |

ますます誤解をしてしまう。

NOR、NAND回路があるからAND回路やOR回路が組める

そして、論理和回路(OR回路)の組み方を見た。

| 論理和回路(OR回路)の組み方 |

|---|

|

|

NOR回路を2個使った場合と、NAND回路を3個使った場合だ。 本当に代用できるのだ。 |

論理演算が頭の体操に思えてきた。 次に論理積(AND回路)の組み方を見た。

| 論理積(AND回路)の組み方 |

|---|

|

|

NAND回路を2個使った場合と、NOR回路を3個使った場合だ。 これも代用回路だ。 |

ところで、NOR回路やNAND回路の記号を見て、各論理回路を組めるのだが 実際のNOR回路やNAND回路の中身は見ていない。 だが、この時点では 一体、どういう回路やろ? と疑問には思わなかった。 回路の中身をブラックボックスにしたまま、前に進んでいった。フリップフロップ回路

フリップフロップとは Flip flop だ。 日本語に直訳すると コロコロ変わる、ばたつく などの意味がある。 なぜ、「flip flop」をいう言葉が適切なのかは後述しています。 本ではフリップフロップ回路の事を以下のように書いていた。

| フリップフロップ回路とは? |

|---|

|

2つの入力端子を持ち、かつ、出力は、2つの安定状態を保っている。 シーソーに例えら、片方が上なら片方が下になり 何か力が加わらないと、そのままの状態を記憶している。 |

わかったような、わからんような表現なので

全く理解できてへん

がバレバレなのだ。

そして、どんな用途については以下のように書いていた。

| フリップフロップ回路の用途 |

|---|

|

記憶したり、数を数えたり、クロックパルスを発生などに 使われている。 |

知りたいのは、SRAMの原理なので、「記憶」に関する事を知りたいのだ。

本を読み進める。

ロジカルオシレーター

言葉の意味を調べないまま、本を読んだ。

| ロジカルオシレーター |

|---|

|

|

否定回路(NOT回路)を使っているため、常に入力信号の反対の値が出力される。 その出力信号が、入力信号になるため、回路を通過すると 反対の信号になる 永遠にHとLがコロコロ変わる回路になっているのだ。 |

ところで否定回路(NOT回路)の中を通過するのに、多少の時間がかかる。 その時間を「t秒」とした場合、以下の事が起こる。

| 否定回路(NOT回路)を通過するのに「t秒」かかる場合 |

|---|

|

|

信号を入力してから、出力されるまでt秒かかる。 その出力信号が、入力信号として回路に送られても 結果が反映されるまでt秒かかる。 そのためt秒間のパルス信号が発生する。 |

この時は気づかなかったが、ロジカルオシレーターは 発信回路 というのだ。 まさにパルスを発生させる回路なのだ。 インバーター回路 次に2連インバーター回路が出てきた。

| 2連インバーター |

|---|

|

|

入力値が一定だと、2つの否定回路の間の部分が、常に一定だ。 否定回路が値を記憶していると。 入力値を変えると、2つの否定回路の間の部分が変化した後、一定になる。 入力値を変える事で、値が切り替わり、その後は安定する回路を フリップフロップだという。 |

これが回路に記憶させる事なのか!

と妙に納得してしまった。

ところで、これを2連インバーターというのか。

全く疑問に思わなかったが、だいぶ後になってわかった。

インバーター(Inverter)は、逆変換の意味がある。

否定回路(NOT回路)の事をインバーターというのだ。

ところで、次の疑問を持った。

| 否定回路の電源は? |

|---|

|

|

入力値が「0」の場合、出力は「1」になる。 出力を「1」にするためには、電源が必要になる。 どこから供給されているのか? |

そんな事が疑問に思った。 あとで、わかった話だが、きちんと電源線があるのだ。

| 否定回路の電源 |

|---|

|

|

記号には入力・出力の線しかないが 実際の否定回路には電源供給の線があるのだ。 |

RSフリップフロップ回路

RSフリップフロップが、フリップフロップ回路の基本形だという。 ところで「R」は「Reset」(リセット)、「S」は「Set」(セット)の意味だ。

| RSフリップフロップ回路 |

|---|

|

|

NAND回路を2つ組み合わせてできる。 入力「S」と「R」の結果は、「Q」と「  」になる。 」になる。「  」は「Q」の反転値になる。 」は「Q」の反転値になる。

|

この回路を見て、ふと思った。

出力結果が、片方の入力値になっているため

どうやって値を決める事ができるのか

という疑問が生まれた。

| 出力結果は、どうやって決まるのか |

|---|

|

|

AのNAND回路の出力結果が、Bの入力値になる。 反対に、BのNAND回路の出力結果が、Aの入力値になる。 なんだか「鶏が先か、卵が先か」のように思える。 |

厄介な問題だ。 だが、色々、ネットで調べてみると、面白い発想を発見した。 回路に個体差があるため 2つ回路の出力時間に時差が生じる そう考えると、非常に、すっきりした。 そして以下のように考える事ができる。 まずは「S」と「R」が共に「0」の場合だ。

| 「S」と「R」が共に「0」の場合 |

|---|

|

|

回路Aよりも回路Bの方が、先に出力すると仮定する。 Rが「0」の場合、もう片方の入力が「0」でも「1」でも NAND回路(B)の出力結果(  )は「1」になる。 )は「1」になる。NAND回路(A)の入力がSが「0」で、もう片方が「1」なので 出力結果(Q)は「1」になる。 |

だが、この場合、Qとの値は、共に「1」になり 同じ値になると具合が悪い。 そのため、この場合の結果は 禁止 と呼び、RSフリップフロップでは扱わない事にしているのだ。 次に「S」が「1」で、「R」が「0」の場合を見てみる

| 「S」が「1」で、「R」が「0」の場合 |

|---|

|

|

先にBのNAND回路が出力結果を出したとする。 Rは「0」なので、Bの出力結果は無条件で「1」になる。 そしてAのNAND回路はSの「1」と「1」の結果なので「0」になる。 |

同じ「S」が「1」で、「R」が「0」の場合でも 先にAのNAND回路の方が出力した場合を考えてみる。

| 「S」が「1」で、「R」が「0」の場合 先にAのNAND回路が結果出力した場合 |

|---|

|

|

先にAのNAND回路が出力した場合、結果は「0」か「1」かは不明だ。 だが、「0」でも「1」であっても、Rが「0」なので BのNAND回路の出力結果は「1」になる。 すると、AのNAND回路が入力がSの「1」と「1」になるので 出力結果は「0」に決まる。 Aが先に出力しても、Bが先に出力しても結果的には Qは「0」で  は「1」になる。 は「1」になる。

|

今度は、「S」が「0」で、「R」が「1」の場合を見てみる

| 「S」が「0」で、「R」が「1」の場合 |

|---|

|

結果はQが「1」で は「0」になる。 は「0」になる。

|

今度は、「S」が「1」で、「R」が「1」の場合を見てみる

| 「S」が「1」で、「R」が「1」の場合 |

|---|

|

|

結果だけ書くと、Aが先に出力するか、Bが先に出力するかで Qと  の値が変わってくる。 の値が変わってくる。どっちになるか、その時次第なのだ。 |

その時次第で出力結果が変わるため、この場合を

不定

と呼ぶのだ。

なぜ、「不定」と呼ぶのか。

その理由は以下の通りなのだ。

| (S,R)の値が(0,1)もしくは(1,0)の場合から (S,R)=(1,1)にしても、出力値は変化しない |

|---|

|

|

不定と呼ばれる理由は、(S,R)の値を(1,1)にしても 出力結果の(Q,  )の値が変化しないからだ。 )の値が変化しないからだ。

|

実際にRSフリップフロップを使って値の変化を見てみる。

| (S,R)の値が(0,1)もしくは(1,0)の場合から (S,R)=(1,1)にしても、出力値は変化しない |

|---|

|

出力結果の(Q, )の値が変化しないのがわかる。 )の値が変化しないのがわかる。

|

入力値と出力値のの表は以下のようになる。

| SとRの入力値と出力値の表 |

|---|

|

だが、思った。 これのどこが記憶装置やねん? 全然、理解できない。 だが、以下のサイトを発見した。 デジタル回路基礎(ラッチ・フリップフロップ) すると・・・ だから記憶装置なのか! と納得できた。 どういう事なのか。 サイトにあったのは、本に書いていたRSフリップフロップ回路に 否定回路を組み込んだ物だ。

| NOT回路(否定回路)を組み込んだRSフリップフロップ回路 |

|---|

|

| S、Rの両方の入力値を反転させる否定回路を組み入れている。 |

この場合、どういう値を取るのか、表にしてみた。

| 入力値と出力値の表 |

|---|

|

入力値の(S,R)と、出力値の(Q,)の値を時系列にすると 非常によくわかる。

入力値の(S,R)と、出力値の(Q, )の値を時系列にする )の値を時系列にする |

|---|

|

|

Sに「1」の値を代入するのは、まるでスイッチを押した感じなる。 スイッチが押されたので、出力値のQが反応して「1」を出力する。 そしてスイッチSの値を「0」に戻しても、Qの値は変化しない。 Qが「1」の値を記憶しているのだ。 Qの値を元の「0」に戻したい場合は、リセットのRを押す(「1」の値にする) すると、Qの値が「0」になる。Rを「0」にしてもQの値は「0」のままだ。 Qが「0」の値を記憶しているのだ。 Sのボタンを押したらQが「1」になり、Rのボタンを押せばQが「0」になる。 |

ところで、RSフリップフロップなのだが、調べている際

以下のサイトを発見した。

【5分で覚えるIT基礎の基礎】デジタル回路の基礎の基礎 第4回 記憶を実現するRSラッチ

もしかして・・・

DRAMの仕組みに出てきたラッチではないか!

| DRAMの仕組み (初期の頃) |

|---|

|

|

行ラッチ、列ラッチは一時的にデータを貯める場所だが ここにRSラッチが使われている。 |

一時的に素早く記憶させるため、記憶回路を組み込む必要があるのだ。D形フリップフロップ回路

DとはDelayの意味で Delayed Flip flop という。 遅延フリップフロップ回路なのだ。 そして同期型フリップフロップとも言われる。 遅延と同期とはどういう事やねん? と思いながら、先に進める事にした。 SRフロップフロップ回路の入力は、セット(S)とリセット(R)だが D形フリップフロップでは、入力(D)とクロック信号(CLK)だ。

| D形フリップフロップ回路 |

|---|

|

入力値(D,CLK)と出力値(Q,)の値を表にしてみた。

| 入力値と出力値 |

|---|

|

|

RSフリップフロップと違い、「禁止」は存在しない。 |

入力値(D,CLK)と出力値(Q,)の値を時系列にしてみた。

| 時系列の表 |

|---|

|

|

Dに「1」の値を入れる(スイッチを入れる)が、その時点ではQの値は変化しない。 クロック信号(CLK)で「1」を送ると、Qの値が「1」に変化する。 その後、Dの値を「0」(スイッチを切る)にしてもQの値は「1」のままだ。 Qの値が記憶されているのだ。 そしてクロック信号(CLK)により、Qの値が「0」に戻る。 クロック信号で同期を取っているのだ。 |

T形フリップフロップ回路

「T」の意味は Toggle(トルグ:状態反転) だ。 実際に、Tフリップフロップ回路が、どういう物か見てみる

| Tフリップフロップ回路 |

|---|

|

| RSフリップフロップ回路を複雑にした感じがする。 |

複雑になったため、Tの値に対して出力の値(Q,)の値を 算出してみようとしたが・・・ 混乱の末、断念・・・ してしまった。 そこで真理表を見ながら、どういう振る舞いをするのか 入力値と出力値を時系列に並べてみた。

| Tフリップフロップの入力値と出力値を時系列で並べてみる |

|---|

|

|

Tからクロック信号が送られる。 クロック信号を発する度に、Qの値が反転する。 |

クロック信号により出力値が反転するから Tフリップフロップ と言うのだ。JKフリップフロップ回路

JKという名前の由来だが、諸説、色々ある。 JK-FFの都市伝説 結構、面白い。他のサイトなども見てみた。 ノーベル物理学賞を受賞した「Jack Kilby」の説が有力のようだ。 少なくとも J(女子)、K(高生)が発明したフリップフロップ回路 ではなさそうだ。 JKフリップフロップ回路は以下の回路になる。

| JKフリップフロップ回路 |

|---|

|

|

RSフリップフロップ回路でS(セット)に当たるのがJ。 R(リセット)に当たるのがKなのだ。 そしてクロック信号を送るCLKがあるのだ。 |

この図を見て思った。

知らへん回路図が出てきた

| 見た事もない回路図 |

|---|

|

|

NAND回路だが、3本足になっている。 一体、どういう回路なのだろうか? |

色々、ネットで調べてみるが、これだという説明がない。

先に進めないやん!

と途方に暮れそうになったのだが、以下のサイトを見て納得した。

論理回路

| 3本足のNAND回路とは |

|---|

|

|

NAND回路の入力値を3つにした物にすぎなかった。 A,B,Cの論理積の否定がDになるのだ。 ベン図で描くと、茶色の領域がDになるのだ。 |

単に3つの値での論理積の否定回路だったので、脱力感だった。

そして、JKフリップフロップ回路をよく見ると

ある事に気づく。

Tフリップフロップそっくりやん!

| JKフリップフロップ回路 |

|---|

|

|

入力のJとKの部分を赤で塗ってみた。 赤い部分をのぞくと、Tフリップフロップ回路になる。 入力値(J,K)が(0,0)の場合、クロック信号を送っても 論理積の否定は「1」になってしまう。 |

そして、(J,K)=(0,0)のJKフリップフロップ回路をよく見ると

ある事に気づく。

RSフリップフロップやん!

| (J,K)=(0,0)の場合のJKフリップフロップ回路 |

|---|

|

|

(R,S)=(1,1)の時のRSフリップフロップ回路と同じになる。 この場合、出力の値(Q,  )は不定になる。 )は不定になる。だが、一度、JやKの値を入力し(Q,  )が決まった後に )が決まった後に(J,K)=(0,0)にしても、出力値は変化しない事を意味する。 |

RSフリップフロップ回路にクロック信号を追加した感じだ。 RSフリップフロップの場合だと、入力値のSやRの値を変化させたら 出力値が変化したが、JKフリップフロップの場合は J,Kの値を変化した後、クロック信号があって、はじめて出力値に反映される。

| (J,K)の値を変化させた後、クロック信号で出力値に反映される |

|---|

|

(J,K)=(1,0)にして、クロック信号を送ると出力値(Q, )=(1,0)になる。 )=(1,0)になる。そして(J,K)=(0,0)にしても、出力は変化しない。記憶されているのだ。 (J,K)=(0,1)にして、クロック信号を送ると出力値(Q,  )=(0,1)になる。 )=(0,1)になる。

|

ところでRSフリップフロップの場合、(S,R)=(1,1)の場合 出力値(Q,)が同じになるため「禁止」という組み合わせで 使わない事になっていた。 JKフリップフロップは、その「禁止」の組み合わせをなくしている。 禁止ではなく、反転なのだ。

| (J,K)=(1,1)の場合、反転をする |

|---|

|

|

(J,K)=(1,1)の場合、クロック信号が送られる度に (Q,  )の値が反転する。 )の値が反転する。

|

論理回路と実際の回路

論理回路の勉強をしている間、実際には、どういう回路なのか 疑問に思っていた上、NAND回路、NOR回路はICに埋め込まれているが AND回路やOR回路は、NAND回路の組み合わせで作っているという 誤解をしていた。 だが、AND回路、OR回路が存在するのか知りたい欲求が勝り 以下のサイトを発見した。 コンピュータの仕組み(電気回路〜基本論理回路) - yokkunsの日記 そして本当にトランジスタを組み合わせてAND回路やOR回路を組んでいるサイトを発見。 トランジスタ・ロジック回路 mosトランジスタを使って論理回路を組んでいる話も発見した。 琉球大学情報工学科 基本論理ゲート 論理ゲートの電気回路 探せばあるやん と思った。

| 論理和回路(OR回路) |

|---|

|

|

トランジスタをスイッチにして論理和回路だ。 XかYに信号(電気)を流すと、トランジスタがスイッチになり トランジスタ内で電気が流れ、その電気が出力部分に流れる。 |

次に論理積だが、論理和と似ている。 ダイオードの向きが逆さまなだけだ。

| 論理積回路(AND回路) |

|---|

|

|

トランジスタをスイッチにして論理積回路だ。 だが、ダイオードが反対方向なので、XとYで電気を流そうにも 電気流れないので、スイッチの役目にはならないのだが・・・ |

いくら考えても・・・

わかるわけ、ねぇーだろ!!

だった。

アッサリ挫折して、次に否定回路を見る。

| 否定回路(NOT回路) |

|---|

|

|

入力部分のXに電気が流れていないと、トランジスタは 電気を流さない。そのため、電源からの電気は全てDへ流れる だが入力Xに電気を流すと、トランジスタがスイッチになる。 Zに流れるはずだった電気を、トランジスタ経由で逃した形になり 結果、Zに電気が流れなくなるというのだ。 |

SRAMの内部構造

論理回路の話を経て、ようやくSRAMの内部構造に迫れるようになった。 SRAMの場合、フリップフロップ回路を使っている。 実の所、フリップフロップ回路やMOS形トランジスタを勉強する前、 以下のサイトなどでSRAMの仕組みを見て、SRAMの事を知ろうとした。 【レポート】メモリ技術解説(1) メモリの基本、SRAM/DRAM | マイナビニュース SRAMは6個のトランジスタを使った記憶装置だという事は知ったが 仕組みや原理については・・・ チンプンカンプン だった。 だが、MOS形トランジスタやフリップフロップ回路を知った上で SRAMの仕組みや構造についてのサイトを見た。 ワード線電位制御の効果を知る:微細化に堪え得るオンチップSRAM (2/3) - EDN Japan コンピュータアーキテクチャの話 (125) マルチポートレジスタ(1) | マイナビニュース 思わず・・・ そんな事だったのか! と、モヤモヤしたいたのが一瞬にして晴れたのだった。 SRAMの仕組みを見ていく事にする。

| SRAMの仕組み |

|---|

|

|

DRAMとの違いは、ビット線が2本ある。 片方は否定回路を入れているので、双方の値は反転した物になっている。 |

そしてRSフリップフロップと見れば、見通しが良くなる。

| SRAMはRSフリップフロップ回路と見れば、わかりやすい |

|---|

|

|

RSフリップフロップ回路では、入力時は、どちらかが「0」で どちらかが「1」になる。 そのためビット線から書き込みの信号(電気)が送られた時 片方に否定回路を組む事で、(S,R)が同じ値になるのを防いでいる。 |

実際にデータの書き込みとなると、以下のようになる。

| データの書き込み |

|---|

|

|

ワード線から電気が送り込まれる事で、スイッチの役目をしている N形MOSトランジスタのスイッチが入る。 ビット線から信号線(電気)が送り込まれる。 |

ワード線の電気を止める。 この場合、RSフリップフロップでは(S,R)=(0,0)の状態になり 入力された値は記憶される。 次に書き込まれたデータの読み込みだ。

| 出力部分について |

|---|

|

|

フリップフロップ回路に記憶したデータを読み出す際 ビット線につながっている部分が出口になる。 出口の部分は出力値(Q,  )と見ればわかりやすい。 )と見ればわかりやすい。

|

データの読み込みの際、ワード線に電気が流れ トランジスタのスイッチが入った状態になる。

| データの読み込み |

|---|

|

|

片方から電気信号が流れる。 もう片方は反転した物なので、電気信号は流れない。 |

論理回路で見たSRAMの仕組みだ。

だが、これだけだと

データの記憶の仕組みがわからん

となる。

そこでトランジスタを使った回路を見て

記憶を保持する原理を見ていく。

| 6個のトランジスタでできた記憶装置 |

|---|

|

|

信号の出し入れの出入口のために2個のトランジスタ。 記憶部分に4つのトランジスタが使われている。 そのうち2個がN-MOSで、残り2個がP-MOSだ。 |

そしてデータの書き込む様子を見てみる

| データの書き込み |

|---|

|

|

ワード線に電気が流れ、スイッチの役目を果たす2個のトランジスタが働き 出入口の門が開く。 そして記憶部分のトランジスタのスイッチの状態が決まる。 |

その結果、電源からの電気が流れ込み、電位があがった状態になる。

| 「1」の場合、電位が上がる |

|---|

|

|

ワード線の電気を止めて、電気の逃げ場をなくす。 赤い線の部分は、電源から電気が流れ込み、電位が上がった部分だ。 この状態を「1」を記憶していると言う。 |

次にデータの読み込みだ。

| データの読み込み |

|---|

|

|

ワード線に電気が流れる。 出入口のトランジスタがの門が開き、電位の高い部分から 電気が流れる事によって、「1」を読み込んだ事になる。 |

SRAMはトランジスタを使って記憶させているため場所を取る。 そのため、高速ではあるが、安価で大容量のメモリが作りにくい問題がある。 現在の所、DRAMにとって代わる話は聞かない。

フラッシュメモリ

メモリでも、USBメモリやデジカメのメモリといった フラッシュメモリの場合、SRAMやDRAMと違い 電源がなくても記憶が維持される。 DRAM、SRAMを調べてみる間に、わかったのは フラッシュメモリは MOSトランジスタで記憶させている という事だ。 だが、力尽きてしまったので、次の機会に取り上げる事にします。

最後に メモリの見方がわからなかったので、これはネタに使えると思い メモリを調べていくと、論理回路や高周波回路の問題点などにぶつかり とんでもない量になりました。 お蔭で、力尽きて、EDO DRAMの仕組みや、フラッシュメモリを省略しました。 載せきれなかった分については、別の機会に載せたいと思います。